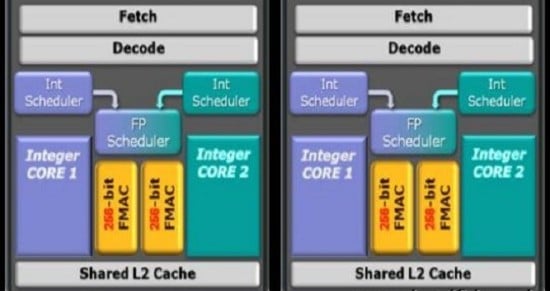

Desde el lanzamiento de los microprocesadores AMD FX de primera generación “Zambezi” basados en la micro-arquitectura Bulldozer, AMD aprovecho la casi nula disponibilidad de aplicaciones que usen el juego de instrucciones AVX de 256 bits, para desarrollar la unidad de punto flotante Flex-FP conformada por 2 unidades FMAC de 128 bits y una unidad MMX/x86, la que se comparte entre las dos unidades de procesamiento de enteros x86 (ALUs) presentes en el módulo Bulldozer.

Flex-XP ha mostrado ser una solución bastante buena hasta el momento, tal es así que se ha mantenido (con algunas mejoras) en las micro-arquitecturas Piledriver y Steamroller, dada la poca adopción de la industria del software de las instrucciones AVX de 256 bits (Flex-FP las procesa en dos partes de 128 bits cada una).

Pero esta situación podría cambiar en los siguientes años, y en documentos publicados por la propia AMD revelan que están trabajando en una nueva unidad de punto flotante de 256 bits, capaz de ejecutar instrucciones AVX de 256 bits en un solo ciclo.

Gracias al soporte completo a 256 bits, el rendimiento de las futuras aplicaciones que usen instrucciones AVX1.0/1.1/2.0 de 256 bits mejorará considerablemente. Se estima que gracias al soporte a operaciones de punto flotante en enteros de AVX 2.0 y superiores, el uso de estas instrucciones deberá empezar a cobrar popularidad entre los desarrolladores de aplicaciones.

Al parecer los futuros microprocesadores y APUs basados en la micro-arquitectura Excavator serán los primeros en usar esta nueva unidad Flex-FP con FMACs de 256 bits, factor que podría coincidir con las enormes mejoras de rendimiento que promete AMD para esta futura micro-arquitectura.

Fuente: Planet 3DNow!