Comunicado de prensa

En el día de la Arquitectura de Intel 2021, Raja Koduri y los arquitectos de Intel proporcionaron detalles sobre dos nuevas arquitecturas de núcleo x86.

La primera arquitectura híbrida de rendimiento de Intel, cuyo nombre en código es «Alder Lake», con el programador inteligente de cargas de trabajo de Intel® Thread Director; “Sapphire Rapids”, el Intel® Xeon® de próxima generación, procesador escalable para el centro de datos; nuevas unidades de procesamiento de infraestructura; y próximas arquitecturas gráficas, incluidas las microarquitecturas Xe HPG y Xe HPC, y los SoC Alchemist y Ponte Vecchio.

Estas nuevas arquitecturas impulsarán los próximos productos de alto rendimiento y establecerán las bases para la próxima era de la innovación de Intel destinada a satisfacer la creciente demanda mundial.

Raja Koduri abordó la importancia del avance arquitectónico para satisfacer esta demanda, diciendo: “La arquitectura es alquimia de hardware y software. Combina los mejores transistores para un motor determinado, conecta a través de paquetes avanzados, integra cachés de alto ancho de banda y bajo consumo de energía y los equipa con memorias de gran capacidad y gran ancho de banda e interconexiones escalables de baja latencia para la informática híbrida agrupaciones en un paquete, a la vez que garantiza que todo el software se acelera sin problemas. … Los avances que divulgados hoy demuestran cómo la arquitectura satisfará la aplastante demanda de más computación rendimiento a medida que las cargas de trabajo desde el escritorio al centro de datos se hacen más grandes, más complejas y más más diverso que nunca «.

Núcleos x86

Núcleo eficiente

La nueva microarquitectura de núcleo eficiente de Intel, anteriormente denominada en código «Gracemont», está diseñada para el rendimiento eficiencia, lo que permite un rendimiento multiproceso escalable para la multitarea moderna. Este es el más eficiente de Intel microarquitectura x86 con un objetivo de área de silicio agresivo para que las cargas de trabajo multinúcleo puedan escalar horizontalmente con el número de núcleos. También ofrece una amplia gama de frecuencias. La microarquitectura y el esfuerzo de diseño enfocado permitir que Efficient-core funcione a bajo voltaje para reducir el consumo total de energía, mientras crea la energía espacio libre para operar a frecuencias más altas. Esto permite que Efficient-core aumente el rendimiento para más cargas de trabajo exigentes.

Efficient-core utiliza una variedad de avances técnicos para priorizar las cargas de trabajo sin desperdiciar potencia de procesamiento y para mejorar directamente el rendimiento con características que mejoran la instrucción por ciclo (IPC), incluso:

- Caché de destino de 5.000 ramas de entrada que da como resultado una predicción de rama más precisa

- Caché de instrucciones de 64 kilobytes para mantener cerca las instrucciones útiles sin gastar memoria del subsistema

- El primer decodificador de longitud de instrucción bajo demanda de Intel que genera información de predescodificación

- Decodificador desordenado agrupado de Intel que permite decodificar hasta seis instrucciones por ciclo mientras manteniendo la eficiencia energética

- Un back-end amplio con asignación de cinco anchos y retiro de ocho anchos, ventana de 256 entradas fuera de orden y 17 puertos de ejecución

- Tecnología de aplicación de flujo de control Intel® y redirección de tecnología de virtualización Intel® Proteccion

- La implementación de AVX ISA, junto con nuevas extensiones para soportar integer artificial operaciones de inteligencia (IA)

En comparación con el núcleo de la CPU Skylake, la microarquitectura de unidad central de procesamiento (CPU) más prolífica de Intel, en rendimiento de un solo hilo, el núcleo eficiente logra un 40% más de rendimiento con la misma potencia o ofrece el mismo rendimiento mientras consume menos del 40% de la energía. Para el rendimiento, los cuatro núcleos eficientes ofrecen un 80% más de rendimiento y, al mismo tiempo, consumen menos energía que dos núcleos Skylake en ejecución cuatro subprocesos o el mismo rendimiento de rendimiento mientras consume un 80% menos de energía.

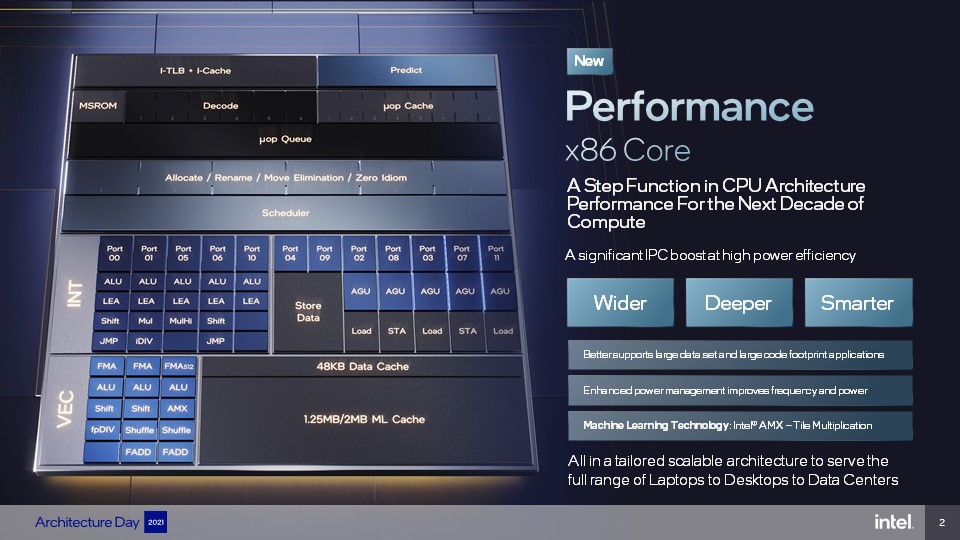

Núcleo de rendimiento

La nueva microarquitectura Performance-core de Intel, anteriormente denominada «Golden Cove», está diseñada para velocidad y empuja los límites de baja latencia y rendimiento de aplicaciones de un solo subproceso. Las cargas de trabajo van creciendo en su huella de código y exigen más capacidades de ejecución. Los conjuntos de datos también están creciendo masivamente junto con los requisitos de ancho de banda de datos. La nueva microarquitectura de Intel Performance-core proporciona una aumento significativo en el rendimiento de propósito general y mejor soporte para aplicaciones de gran tamaño de código.

El Performance-core presenta una arquitectura más amplia, profunda e inteligente:

- Más amplio: seis decodificadores (en vez de cuatro); caché µop de ocho anchos (en vez de seis); seis asignaciones (de cinco); 12 puertos de ejecución (hasta 10)

- Más profundo: archivos de registro físico más grandes; búfer de reordenamiento más profundo con 512 entradas

- Más inteligente: precisión mejorada en la predicción de ramas; latencia L1 efectiva reducida; predictivo de escritura completa optimizaciones de ancho de banda en L2

El núcleo de rendimiento es el núcleo de CPU de mayor rendimiento que Intel haya construido jamás y supera los límites de los bajos latencia y rendimiento de aplicaciones de un solo subproceso con:

- Una mejora de Geomean de ~ 19% en una amplia gama de cargas de trabajo sobre la actual 11a generación de Intel® Arquitectura de procesador Core ™ (Cypress Cove) a frecuencia ISO para rendimiento de uso general

- Exposición a un mayor paralelismo y un aumento en el paralelismo de ejecución

- Intel® Advanced Matrix Extensions, el avance de aceleración de IA integrado de próxima generación, para inferencia de aprendizaje profundo y rendimiento del entrenamiento. Incluye hardware dedicado y nueva arquitectura de conjunto de instrucciones para realizar operaciones de multiplicación de matrices significativamente más rápido.

- Latencia reducida y mayor compatibilidad con aplicaciones de gran tamaño de datos y código.

Cliente

SoC de cliente de Alder Lake

La arquitectura de cliente de próxima generación de Intel, cuyo nombre en código es Alder Lake, es el primer híbrido de rendimiento de Intel arquitectura, que por primera vez integra dos tipos principales: Performance-core y Efficient-core, para rendimiento significativo en todos los tipos de cargas de trabajo. Alder Lake se basa en el proceso Intel 7 y es compatible con la memoria más reciente y la E / S más rápida.

Alder Lake ofrecerá un rendimiento increíble que se escala para admitir todos los segmentos de clientes desde ultraportátiles computadoras portátiles a computadoras de escritorio comerciales y entusiastas al aprovechar un único sistema en chip (SoC) altamente escalable arquitectura con tres puntos clave de diseño:

- Una computadora de escritorio con zócalo de máximo rendimiento, dos chips con desempeño líder, eficiencia energética, memoria y E / S.

- Un paquete BGA móvil de alto rendimiento que agrega imágenes, gráficos Xe más grandes y Thunderbolt 4 de conectividad

- Un paquete delgado, de baja potencia y alta densidad con E / S optimizadas y suministro de energía.

El desafío de construir una arquitectura tan escalable es satisfacer las increíbles demandas de ancho de banda de los agentes informáticos y de E / S sin comprometer la potencia. Para resolver este desafío, Intel ha diseñado tres tejidos independientes, cada uno con heurísticas en tiempo real basadas en la demanda:

- La estructura informática puede admitir hasta 1000 gigabytes por segundo (GBps), que son 100 GBps por núcleo o por clúster y conecta los núcleos y gráficos a través del caché de último nivel a la memoria

- Cuenta con un rango de frecuencia dinámico alto y es capaz de seleccionar dinámicamente los datos ruta para la latencia frente a la optimización del ancho de banda en función de las cargas de tejido reales

- Ajusta dinámicamente la política de caché de último nivel, inclusiva o no inclusiva, según utilización

- La estructura de E / S admite hasta 64 GBps, conectando los diferentes tipos de E / S, así como internos. dispositivos y puede cambiar la velocidad sin problemas sin interferir con el funcionamiento normal de un dispositivo, seleccionar la velocidad de la tela para que coincida con la cantidad requerida de transferencia de datos

- La estructura de memoria puede entregar hasta 204 GBps de datos y escalar dinámicamente su ancho y velocidad de bus para admitir múltiples puntos operativos para un ancho de banda alto, baja latencia o baja potencia.

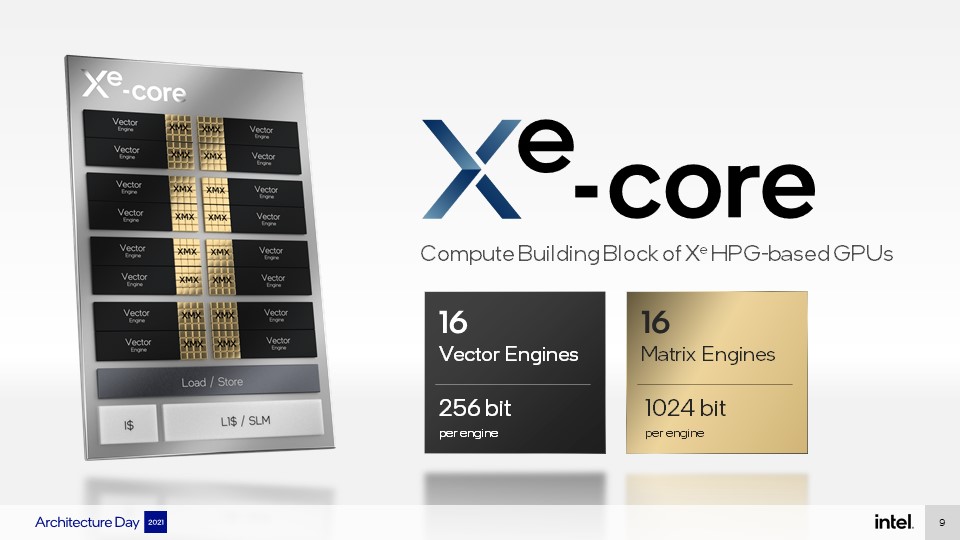

SoC de microarquitectura y alquimista Xe HPG

Xe HPG es una nueva microarquitectura de gráficos discretos diseñada para escalar al rendimiento de clase entusiasta para cargas de trabajo de juegos y creación. La microarquitectura Xe HPG impulsa la familia Alchemist de SoCs, y el Los primeros productos relacionados saldrán al mercado en el primer trimestre de 2022 bajo la marca Intel® Arc ™. El Xe La microarquitectura HPG presenta un nuevo Xe -core, un elemento escalable, programable y centrado en la computación.

La hoja de ruta de gráficos del cliente incluye Alchemist (anteriormente conocido como DG2), Battlemage, Celestial y Druid SoCs. Durante la presentación, Intel proporcionó detalles de microarquitectura y demostraciones compartidas que se ejecutan en un SoC Alchemist de preproducción, que muestra un juego real, una prueba de estado de Unreal Engine 5 y una nueva versión basada en neuronas.

Super tecnología de muestreo llamada Xe SS.

Los SoC Alchemist, basados en la microarquitectura Xe HPG, están diseñados para ofrecer una gran escalabilidad y

Compute la eficiencia con características arquitectónicas clave:

- Hasta ocho cortes de render con función fija diseñada para DirectX 12 Ultimate

- Nuevo Xe -núcleos con 16 motores vectoriales y 16 motores matriciales (denominados XMX – Xe Matrix eXtensions), caché y memoria local compartida

- Nuevas unidades de trazado de rayos compatibles con DirectX Raytracing (DXR) y Vulkan Ray Tracing Elevación de frecuencia de 1.5x y mejora de rendimiento / vatio de 1.5x en comparación con la microarquitectura Xe LP mediante una combinación de arquitectura, diseño lógico, diseño de circuitos, tecnología de procesos y software optimizaciones

Fabricado en el nodo de proceso N6 de TSMC, un aspecto fundamental de los esfuerzos gráficos de Intel es un enfoque centrado en el software:

- La arquitectura Xe se está diseñando en estrecha colaboración con los desarrolladores, impulsando la alineación estándares de la industria

- La primera unidad de procesamiento de gráficos (GPU) para juegos de alto rendimiento de Intel prioriza el rendimiento y calidad a través de un diseño de controlador que cubre productos gráficos integrados y discretos en un solo base de código

- Intel ha completado una nueva arquitectura de los componentes principales del controlador de gráficos, específicamente la memoria, administrador y compilador, lo que resulta en un rendimiento mejorado para los títulos vinculados a la CPU en un 15% (y tanto como 80%) y mejoró los tiempos de carga del juego en un 25%

Xe SS

XeSS aprovecha la aceleración XMX AI incorporada de Alchemist para ofrecer una nueva tecnología de mejora que permite imágenes de alto rendimiento y alta fidelidad. Utiliza el aprendizaje profundo para sintetizar imágenes cercanas a la calidad del renderizado nativo de alta resolución. Con Xe SS juegos que, solo se podrían jugar a niveles más bajos con configuraciones de calidad o las resoluciones más bajas, pueden funcionar sin problemas con configuraciones y resoluciones de mayor calidad.

- Xe SS funciona reconstruyendo detalles de subpíxeles a partir de píxeles vecinos, así como cuadros anteriores compensados por movimiento

- La reconstrucción la realiza una red neuronal entrenada para ofrecer un alto rendimiento y una gran calidad, con un aumento de rendimiento de hasta el doble

- Xe SS ofrece supermuestreo basado en IA en un amplio conjunto de hardware, incluidos gráficos integrados, por aprovechando el conjunto de instrucciones DP4a

- Varios desarrolladores de juegos iniciales están comprometidos con Xe SS, y el SDK para la versión inicial de XMX será disponible para ISV este mes, con la versión DP4a disponible más adelante este año